86-0755-27838351

GHz世界中的速度加劇晶體信號問題

一個動態(tài)是技術(shù)市場不斷前進,處理器和端點外設(shè)控制器的速度始終更快,并且GHz時鐘是常態(tài),與此同時,IC通過工藝縮小和更小的特征尺寸將更多的石英晶體管封裝到相同尺寸的芯片上,較小的晶體管在較低的電壓下工作,提供較低的輸出驅(qū)動能力,并且無法沿長或高阻抗線移動信號,在碰撞過程中有兩組動力學(xué)在主板線,電纜,連接器和芯片組上經(jīng)常被忽視的技術(shù)細節(jié)-信號完整性-比以往任何時候都更加重要.

當(dāng)時鐘和開關(guān)速度達到數(shù)百兆赫茲時,在10/100以太網(wǎng),USB2.0,SCSI,PCI等標(biāo)準中實現(xiàn)的數(shù)字信號表現(xiàn)得如預(yù)期,并且系統(tǒng)按照規(guī)范運行,將撥號盤旋轉(zhuǎn)到千兆赫范圍,晶振信號完整性成為設(shè)計師的主要問題,較小的移動設(shè)備塞滿了最新的高速處理器和I/O接口,再加上芯片縮小的千兆赫茲處理器和外設(shè),平均信號由于損耗,交叉耦合以及低成本的PCB和連接器而受到衰減消費者價格點.

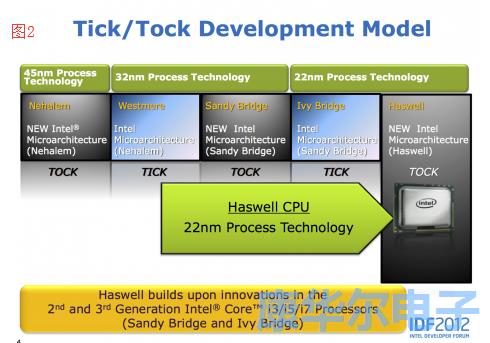

解決這些技術(shù)挑戰(zhàn)的靈丹妙藥是轉(zhuǎn)發(fā)器或轉(zhuǎn)接驅(qū)動器設(shè)備,添加到信號通道的這種便宜的奇跡驅(qū)動FR4上的更長跡線,通過柔性/帶狀電纜,跨越背板,并在所有高速開放標(biāo)準接口中滿足眼圖邊緣,讓我們首先檢查創(chuàng)建信號完整性挑戰(zhàn)的動態(tài),然后看看轉(zhuǎn)接驅(qū)動器如何解決石英晶體振蕩器信號完整性問題,英特爾的路線圖體現(xiàn)了快速的芯片縮減,從2007年的45納米變?yōu)榻裉斓?/span>22納米(圖1),例如,Core Duo取代了流行的Pentium處理器,采用65nm光刻技術(shù),而今天的第4代Core i7(Haswell)器件則采用22nm工藝(圖2).

如圖3所示,從32nm的平面晶體管向更快的三維22nm三柵極(FinFET)MOSFET的移動將柵極電壓降低了20%,降至0.8V左右,英特爾極小的22nmFinFET三維工藝封裝每立方芯片毫米更多晶體管,但工作柵極電壓降低了0.2V,這降低了20%,并且I/O的振蕩器輸出驅(qū)動能力也相應(yīng)降低,如以太網(wǎng),PCIExpress,USB 3.0,SATA3.0,SAS2.0/3.0和DDR內(nèi)存,在三年內(nèi),英特爾預(yù)計到2019年將推出7納米晶體管,它們可能只需要今天的Vdd電壓,輸出驅(qū)動能力將受到更大影響.

影響信號完整性的另一個動態(tài)是從桌面計算到移動設(shè)備的平臺競爭,其中平板電腦,智能手機,2:1(平板電腦和獨立鍵盤)和可穿戴設(shè)備正在萎縮地縮小平臺及其內(nèi)部電路板,器件比以往任何時候都更接近,帶有短截線和埋入式過孔的多層板很難鋪設(shè)高扇出SoC和外圍設(shè)備,節(jié)省空間通常會在柔性電路甚至堆疊芯片多石英晶振模塊上安裝非平凡的IC-或者哪里有空位,在移動平臺中,盡管外部尺寸較小,但可以實現(xiàn)長而中斷的走線長度,路由占據(jù)了房地產(chǎn)的后座,如果完全考慮信號完整性通常是第三優(yōu)先級.

移動設(shè)備還有另一個獨特的挑戰(zhàn),即極其密集的微型母板和子板在窄間距軌跡上傳輸千兆赫信號,由于接近和皮膚效應(yīng)會發(fā)生交叉耦合,在如此小的空間中,多個分布式時鐘線將拾取噪聲,因為源時鐘晶體不能總是靠近收發(fā)器IC,從而導(dǎo)致數(shù)據(jù)線上的隨機抖動,這種抖動將與數(shù)據(jù)信號同時運行,對FR4損耗和阻抗不匹配已經(jīng)不利影響的信號完整性產(chǎn)生不利影響.